VHDL和Verilog的目的相同,但大多数工程师更喜欢其中一种语言。我想知道谁更喜欢哪种语言。

关于Verilog和VHDL之间的区别,有许多神话和常见智慧。(ASIC / FPGA,欧洲/美国,商业/国防等)如果你四处问问,人们会反复告诉你同样的事情,但我想知道这些神话是否基于现实。

所以我的问题是:是否有人可以提供数量化的数据来源,表明谁使用VHDL和谁使用Verilog?再次强调,我寻找的是数字,而不是直觉和一般性指示。

VHDL和Verilog的目的相同,但大多数工程师更喜欢其中一种语言。我想知道谁更喜欢哪种语言。

关于Verilog和VHDL之间的区别,有许多神话和常见智慧。(ASIC / FPGA,欧洲/美国,商业/国防等)如果你四处问问,人们会反复告诉你同样的事情,但我想知道这些神话是否基于现实。

所以我的问题是:是否有人可以提供数量化的数据来源,表明谁使用VHDL和谁使用Verilog?再次强调,我寻找的是数字,而不是直觉和一般性指示。

VHDL和Verilog都是相对较新且相对专业的语言。这两个特点使得它们的定性数据难以获得。另一方面,我们可以利用这些特点来获取优势。我们可以根据可用参考文献的数量尝试推断这些语言的流行程度。

按主题分类的Amazon.com图书列表

VHDL 315

Verilog 132

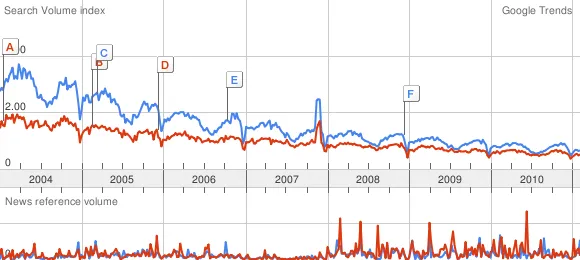

Google趋势:Verilog(红色)vs VHDL(蓝色) -

来源

根据这些数字(仅限这些数字),VHDL似乎比Verilog更为广泛使用;但是,没有显示每个市场份额的详细信息。

我既没有数字,也没有任何直觉。以下是有关VHDL的一些事实。

[1] SystemVerilog提高了Verilog-HDL的能力,使其与VHDL(STD. 1076-2002)的现有能力相当。

[2] VHDL 2008(STD. 1076-2008):是否有人使用最新标准?请使用它,然后与Verilog(STD. 1364-2005)进行比较。

[3] SystemVerilog通过添加丰富的用户定义类型系统并在用户定义类型的领域特别增加强类型能力来扩展Verilog-HDL。 ... 但是,VHDL中的类型检查强度仍然超过SystemVerilog中的类型检查强度。 ... 强类型的缺点在于性能;即编译和模拟(仅在启用运行时检查时)较慢。考虑到项目的投资量(我们公司的理由),缓慢的编译不是问题。

我认为VHDL是一种“安全”的语言,而Verilog是一种让你快速编写模型的“快速”语言。我工作的公司更喜欢安全而不是速度;因此,在我们的设计流程中,我们主要使用VHDL。

还请查看新的OS-VVM(开源VHDL验证方法)发展。