我希望将输入信号延迟一个完整的时钟周期。

我有下面的代码,基本上尝试在时钟的posedge处更改信号。

但是,测试台显示它并不总是延迟1个周期。

在某些情况下,它会在输入信号更改的同时更改。

是否有任何解决此类问题的方法?

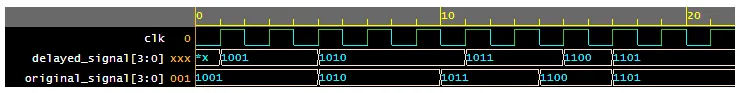

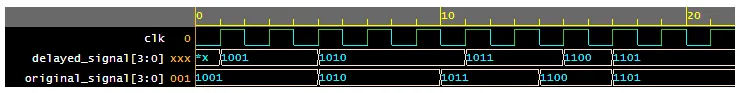

这是波形图: 该波形图显示了输入信号在时钟边沿变为1010时,输出也同时发生变化。

该波形图显示了输入信号在时钟边沿变为1010时,输出也同时发生变化。

但是,延迟信号实际上并没有延迟到下一个周期!

我有下面的代码,基本上尝试在时钟的posedge处更改信号。

但是,测试台显示它并不总是延迟1个周期。

在某些情况下,它会在输入信号更改的同时更改。

是否有任何解决此类问题的方法?

module delay_one_cycle(

input clk,

input[3:0] original_signal,

output reg[3:0] delayed_signal

);

always @(posedge clk) begin

delayed_signal <= original_signal;

end

endmodule

module delay_one_cycle_tb();

reg clk;

reg[3:0] original_signal;

wire[3:0] delayed_signal;

delay_one_cycle doc_inst (clk, original_signal, delayed_signal);

// Initial setup

initial begin

clk = 0;

original_signal = 4'd9;

#5 original_signal = 4'd10;

#5 original_signal = 4'd11;

#4 original_signal = 4'd12;

#3 original_signal = 4'd13;

// finish the simulation

#5 $finish;

end

// clock

always begin

#1 clk = !clk;

end

endmodule

这是波形图:

该波形图显示了输入信号在时钟边沿变为1010时,输出也同时发生变化。

该波形图显示了输入信号在时钟边沿变为1010时,输出也同时发生变化。但是,延迟信号实际上并没有延迟到下一个周期!

- 单个语句@(posedge clk);的作用是什么?我只见过这样的语法:always @ (posedge clk) begin .... end。

- 它是什么类型的结构,如何与上面的repeat配合使用?例如:repeat (5) @(posedge clk);

- 在上述代码中,是否需要同时使用repeat (5) @(posedge clk);和非阻塞赋值(<=)才能获得正确的模拟结果?

- user3330840