假设您有一个被定义如下的信号:

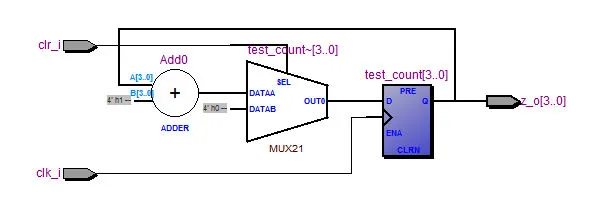

现在,如果测试计数器在模拟过程中低于0或高于11,将立即导致模拟崩溃。我想知道的是,在综合时会发生什么?如果测试计数器增加到11以上或减少到0以下会发生什么?综合工具会强制该信号进行循环吗?请注意,我选择了一个不容易回归到0000的示例。

signal test_count : integer range 0 to 11;

现在,如果测试计数器在模拟过程中低于0或高于11,将立即导致模拟崩溃。我想知道的是,在综合时会发生什么?如果测试计数器增加到11以上或减少到0以下会发生什么?综合工具会强制该信号进行循环吗?请注意,我选择了一个不容易回归到0000的示例。