在微处理器和/或操作系统中,16位、32位和64位体系结构是什么意思?

对于微处理器而言,它是否表示通用寄存器的最大大小,或者整数的大小,或者地址线的数量,或者数据总线线数等内容?

当我们说"DOS是一个16位操作系统"、"Windows是一个32位操作系统"等时,这意味着什么?

在微处理器和/或操作系统中,16位、32位和64位体系结构是什么意思?

对于微处理器而言,它是否表示通用寄存器的最大大小,或者整数的大小,或者地址线的数量,或者数据总线线数等内容?

当我们说"DOS是一个16位操作系统"、"Windows是一个32位操作系统"等时,这意味着什么?

以下是我的原始答案,如果您想了解评论,请参阅。

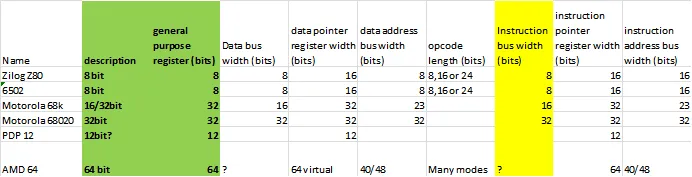

正如您所说,有各种各样的措施。幸运的是,对于许多CPU,许多措施都是相同的,因此不会产生混淆。让我们看一些数据(抱歉,我无法在markdown中找到好的表格方式)。

正如您所看到的,许多列都是很好的候选项。然而,我认为通用寄存器的大小(绿色)是最常见且易于理解的答案。

当处理器在不同寄存器的大小上差异很大时,通常会进行更详细的描述,例如Motorola 68k被描述为16/32位芯片。

其他人认为指令总线宽度(黄色)也符合表格。然而,在今天的流水线世界中,我认为对于大多数应用程序而言,这比通用寄存器的大小要少关键得多。

不同的人可能意味着不同的事情,因为正如你所说有几个措施。例如,谈论内存寻址的人可能与谈论整数算术的人意思不同。然而,我会尝试定义我认为是共同理解的。

我的看法是对于CPU来说,它意味着“用于标准操作的典型寄存器的大小”或“数据总线的大小”(两者通常是等效的)。

我用以下逻辑来证明这一点。Z80具有8位累加器和8位数据总线,同时具有16位内存寻址寄存器(IX、IY、SP、PC)和16位内存地址总线。Z80被称为8位微处理器。这意味着人们通常必须指的是主整数算术大小或数据总线大小,而不是内存寻址大小。

它不是指令的大小,因为Z80(再次)具有1、2和3字节的指令,虽然多字节指令当然是通过多次读取来读取的。在另一个方向上,8086是一个16位微处理器,可以读取8或16位指令。因此,我不同意那些说它是指令大小的答案。

对于操作系统,我会将其定义为“代码编译为在该大小的CPU上运行”,因此32位操作系统具有编译为在32位CPU上运行的代码(根据上述定义)。

区别在于通用寄存器接收的指令集位宽不同。16位可以同时操作2个字节,64位可以一次性操作8个字节的指令。通过每个时钟周期执行更密集的指令,可以经常提高处理器的吞吐量。

这些定义更多是营销术语,而不是精确的技术术语。

在模糊的技术术语中,它们更多地与架构可见宽度相关,而不是任何真正的实现寄存器或总线宽度。例如,68008被归类为32位CPU,但硅片上只有16位寄存器和8位数据总线以及20多个地址位。

http://en.wikipedia.org/wiki/64-bit#64-bit_data_models 数据模型意味着语言的位数。

“操作系统是x位”的短语通常意味着该操作系统是为x位CPU模式编写的,也就是说,64位Windows在x86-64上使用长模式,其中寄存器为64位,地址空间为64位,并且与32位模式有其他明显的区别,其中通常寄存器宽度为32位,地址空间为32位。在x86上,32位和64位模式之间的主要区别是32位中存在分段以实现历史兼容性。

通常,操作系统是根据CPU位数编写的,x86-64是几十年向后兼容性的一个显著例子 - 您可以拥有从16位实模式程序到32位保护模式程序再到64位长模式程序的所有内容。

此外,还有不同的虚拟化方式,因此您的程序可能会像在32位模式下一样运行,但实际上它是由非x86核心执行的。

void* p = something;

int i = (int)p;

这段代码在64位系统上将会崩溃(在32位系统上可以运行),因为void*现在比int大了两倍。

在大多数编程语言中,你不需要过多关注你所使用的系统的位宽。

当我们在计算机科学中谈论2^n位架构时,基本上是在谈论内存寄存器、地址总线大小或数据总线大小。 2^n位架构背后的基本概念是表示这里的2^n位数据可以用来处理大小为2^n的数据。