完整的硬件参考

您可以在01.org找到Intel图形控制器的完整文档:

硬件规格说明-PRMs 作者:Paul Parenteau 最后修改日期:2020年6月15日

回答问题2:是的,有单独的汇编指令,如下所述(来自“GEN汇编简介”)

英特尔GPU汇编的一般格式

通常,所有指令都具有以下形式:

[(pred)] opcode (exec-size|exec-offset) dst src0 [src1] [src2]

(pred) 是可选的谓词。我们现在要跳过它。

opcode 是指令的符号,例如add或mov(下面有完整的指令表)。

exec-size 是指令的SIMD宽度,我们的架构可以是1、2、4、8或16。在SIMD32编译中,通常会将两条执行大小为8或16的指令组合成一条。

exec-offset 是告诉EU哪个ARF寄存器读取或写入的部分,例如(8|M24)会查阅执行掩码的位24-31. 当发出类似下面的SIMD16或SIMD32代码时:

mov (8|M0) r11.0<1>:q r5.0<8

mov (8|M8) r13.0<1>:q r6.0<8

mov (8|M16) r15.0<1>:q r9.0<8

mov (8|M24) r17.0<1>:q r10.0<8

SIMD32汇编的mov指令

由于GRF每个操作数只能访问有限数量的字节,编译器必须发出四个8宽度操作。

dst 是目标寄存器

src0 是源寄存器

src1 是一个可选的源寄存器。注意,它也可以是一个立即值,比如 0x3F000000:f (0.5) 或 0x2A:ud (42)。

src2 是一个可选的源寄存器。

通用寄存器文件(GRF)寄存器

每个线程都有一个专用的空间,包含r0到r127共128个寄存器。每个寄存器为256位或32字节。

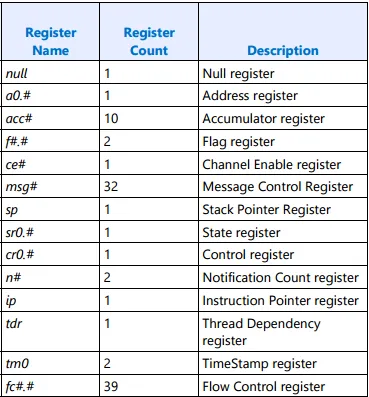

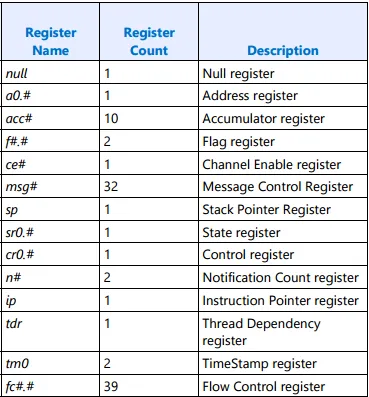

体系结构寄存器文件(ARF)寄存器

在上面的汇编代码中,我们只看到了其中一个特殊寄存器,即空寄存器。通常用于写入和指示线程结束的send指令的目的地。这里是其他体系结构寄存器的完整表格:

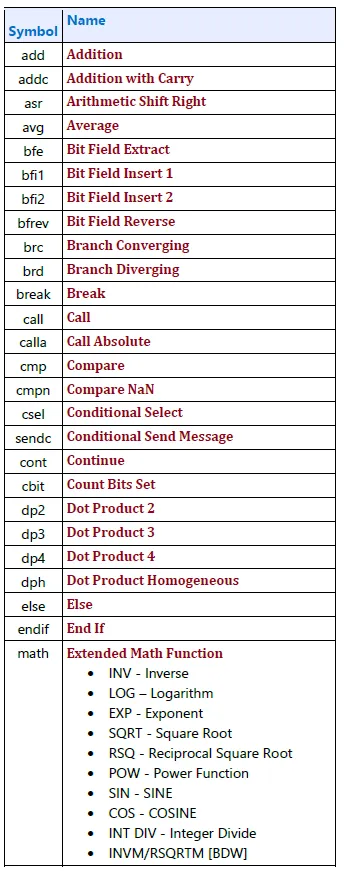

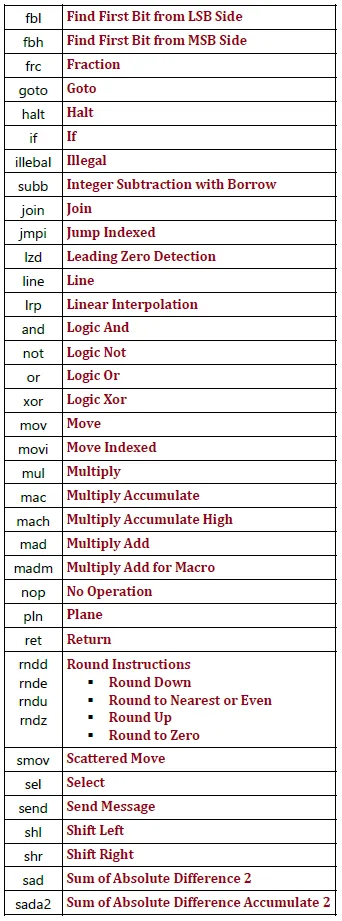

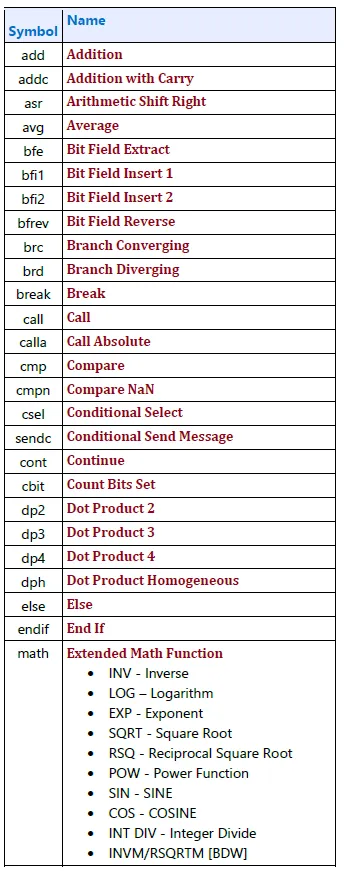

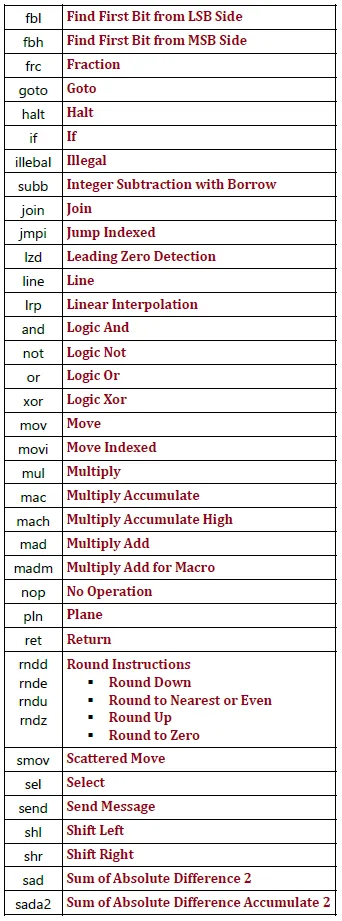

可用的GEN(通用)汇编指令