如果一个32位操作系统采用分段式内存模型,它们仍然会有4GB的限制吗?

我正在阅读《英特尔奔腾处理器系列开发人员手册》,它指出,在分段式内存模型下,可以映射多达64TB的内存。

“在内存组织的分段模型中,逻辑地址空间由多达16,383个最大为4GB的段组成,或者总共最大为2^46字节(64TB)。处理器通过第11章描述的地址转换机制将这64TB逻辑地址空间映射到物理地址空间。应用程序员可以忽略此映射的详细信息。分段模型的优点在于可以单独检查每个地址空间内的偏移量,并且可以单独控制对每个段的访问。”

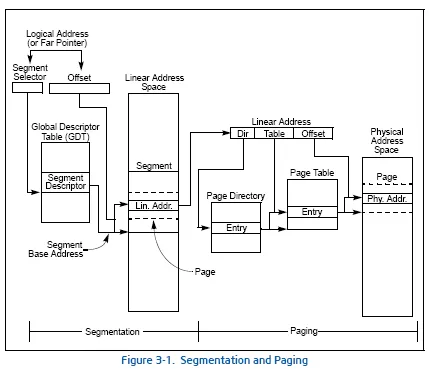

段寄存器不应被视为传统实模式的意义。段寄存器作为全局描述符表的选择器。

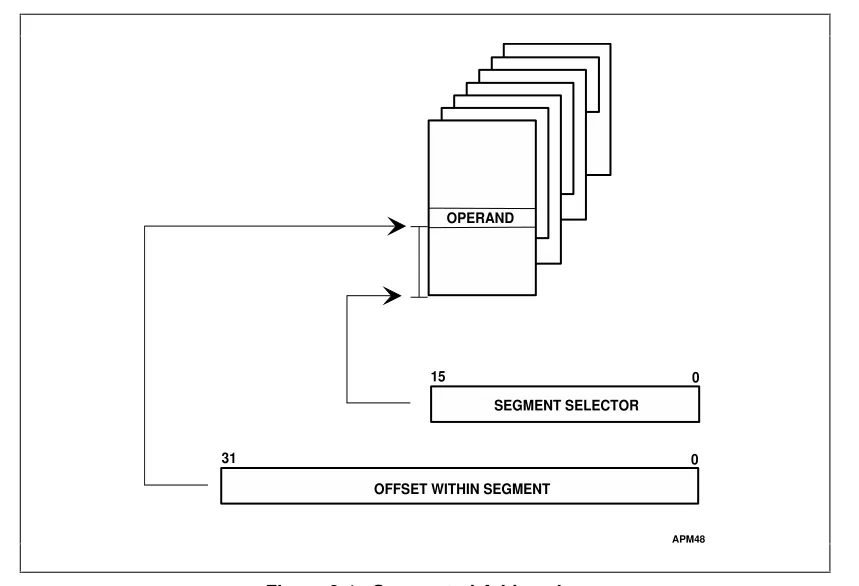

在保护模式下,您使用形式为A:B的逻辑地址来寻址内存。与实模式类似,A是段部分,B是该段内的偏移量。保护模式下的寄存器限制为32位。32位可以表示0到4Gb之间的任何整数。因为B可以是0到4Gb之间的任何值,所以我们的段现在具有最大4Gb的大小(与实模式的推理相同)。现在的区别在于,在保护模式下,A不是段的绝对值。在保护模式下,A是一个选择器。选择器表示全局描述符表(GDT)中的偏移量。GDT包含描述符列表。每个描述符都包含描述段特性的信息。

段选择器提供了无法通过分页实现的额外安全性。

这两种方法[分段和分页]都有各自的优点,但是分页要好得多。尽管分段仍然可用,但作为内存保护和虚拟内存的一种方法,它正在迅速变得过时。事实上,x86-64体系结构需要一个平面内存模型(一个基地址为0,限制为0xFFFFFFFF的段)才能正常运行某些指令。 然而,分段是完全内置在x86架构中的。这是不可能绕开的。因此,在这里,我们将向您展示如何设置自己的全局描述符表——一个段描述符列表。 正如之前提到的,我们将尝试建立一个平面内存模型。段的窗口应该从0x00000000开始,并延伸到0xFFFFFFFF(内存的末尾)。然而,分段可以做到分页所不能做的一件事,那就是设置环级别。

我正在阅读《英特尔奔腾处理器系列开发人员手册》,它指出,在分段式内存模型下,可以映射多达64TB的内存。

“在内存组织的分段模型中,逻辑地址空间由多达16,383个最大为4GB的段组成,或者总共最大为2^46字节(64TB)。处理器通过第11章描述的地址转换机制将这64TB逻辑地址空间映射到物理地址空间。应用程序员可以忽略此映射的详细信息。分段模型的优点在于可以单独检查每个地址空间内的偏移量,并且可以单独控制对每个段的访问。”

更新:

http://pdos.csail.mit.edu/6.828/2005/readings/i386/c05.htm

段寄存器不应被视为传统实模式的意义。段寄存器作为全局描述符表的选择器。

在保护模式下,您使用形式为A:B的逻辑地址来寻址内存。与实模式类似,A是段部分,B是该段内的偏移量。保护模式下的寄存器限制为32位。32位可以表示0到4Gb之间的任何整数。因为B可以是0到4Gb之间的任何值,所以我们的段现在具有最大4Gb的大小(与实模式的推理相同)。现在的区别在于,在保护模式下,A不是段的绝对值。在保护模式下,A是一个选择器。选择器表示全局描述符表(GDT)中的偏移量。GDT包含描述符列表。每个描述符都包含描述段特性的信息。

段选择器提供了无法通过分页实现的额外安全性。

这两种方法[分段和分页]都有各自的优点,但是分页要好得多。尽管分段仍然可用,但作为内存保护和虚拟内存的一种方法,它正在迅速变得过时。事实上,x86-64体系结构需要一个平面内存模型(一个基地址为0,限制为0xFFFFFFFF的段)才能正常运行某些指令。 然而,分段是完全内置在x86架构中的。这是不可能绕开的。因此,在这里,我们将向您展示如何设置自己的全局描述符表——一个段描述符列表。 正如之前提到的,我们将尝试建立一个平面内存模型。段的窗口应该从0x00000000开始,并延伸到0xFFFFFFFF(内存的末尾)。然而,分段可以做到分页所不能做的一件事,那就是设置环级别。

-http://www.jamesmolloy.co.uk/tutorial_html/4.-The%20GDT%20and%20IDT.html

一个 GDT 例如列出了各个用户的访问级别和内存访问区域: 样例 GDT 表格GDT[0] = {.base=0, .limit=0, .type=0};

// Selector 0x00 cannot be used

GDT[1] = {.base=0, .limit=0xffffffff, .type=0x9A};

// Selector 0x08 will be our code

GDT[2] = {.base=0, .limit=0xffffffff, .type=0x92};

// Selector 0x10 will be our data

GDT[3] = {.base=&myTss, .limit=sizeof(myTss), .type=0x89};

// You can use LTR(0x18)

http://wiki.osdev.org/GDT_Tutorial#What_should_i_put_in_my_GDT.3F

分页部分是映射到物理内存的部分。(PAE) 可以提供额外的内存,最多可达64GB。

简而言之,答案是否定的,您不能拥有超过4GB的逻辑内存。我认为在《英特尔奔腾处理器家族开发人员手册》中声称可以达到64TB是印刷错误。